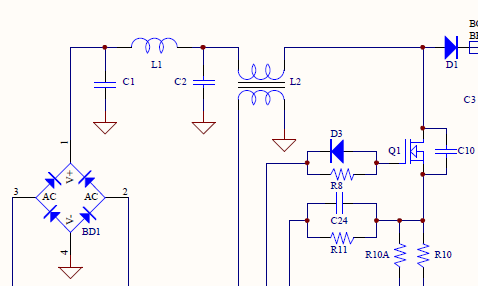

近年来,随着国际能效标准要求的不断提高,常规的肖特基二极管整流无法满足在低压大电流输出规格的能效要求(美国 DoE Level VI,欧盟CoC V5 Tier 2);即使用超低Vf肖特基二极管整流,有的也要增加散热片,如此就会导致PCB 空间大,功率密度小,效率低,外壳温度高;用户手感体验性差等。使用同步整流MOS,在相同输出电流的情况下,损耗非常小,极大地提升了整机的转换效率。

开关电源的工作模式较多(CCM,DCM,QR,BURST),并且同步整流控制IC都是被动接收同步方式,因此很难避免在任何负载及全电压输入条件下故障发生,以下是一些常见问题及改善对策

1:MOS管提前开通或关断

产生原因:

1)SR IC_gate驱动输出受干扰导致提前开通

2)SR IC内部斜率检测电路受干扰,会出现提前开通,或在第一个Ring开通

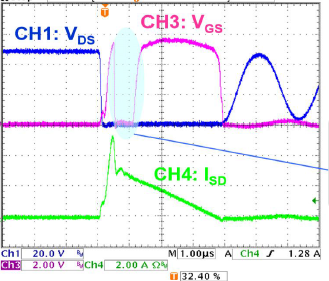

3)SR IC_gate开通后受初级漏感和MOS的DS电容振荡干扰而误触发关断MOS

产生影响:

1)SR MOS的Gate被提前关断,会导致体内二极管导通时间长,效率低,同步MOS温度高。

2)从初级Vds或次级Vds看波形,会有大小波出现(针对CCM模式)。

解决对策:

1) 选择好的SR IC品牌

2) 改善PCB layout(针对外推MOS的SRIC)

3) 调整初级吸收RCD电路,比如吸收二极管串一个阻尼电阻

2:初次级MOS共通问题

产生原因:

在CCM中,当初级MOS开启时,次级MOS应该要及时准确的关断,当次级MOS关断延时太长,存在初次级MOS共通的可能

产生影响:

次级会产生很大的反向电流,严重会损坏MOS

解决对策:

1) 选择Turn-off Time Delay时间非常短的SR IC

2) 选择合适的SR MOSFET(使用较小的Qg)

3) 加大Q1_Gate驱动电阻,减慢其驱动速度

4) 设计恰当的次级RC吸收回路参数

3:输出电压下降,纹波大,带载能力下降

产生原因:

(针对PSR 架构下的同步整流应用)针对在高压230Vac条件下其工作频率去到80KHz或以上的PSR IC方案(BCM/QR,频率限制在110KHz),当电源系统工作在低压115V (实际从170Vac以下电压都有机会出现输出掉坑问题。同步MOS没打开,体内二极管已经工作,导致输出电压下降(一个PN结压降)。

产生影响:

Vout输出电压掉坑,不稳定,纹波大,严重情况下会导致输出电压直接掉到4.2-4.5V,输出电流也下降(只能带到满载的1/2 or 2/3)

解决对策:

1) 把变压器感量调低, 降低工作频率到80KHz以下会有部分改善,但不能完全解决这个问题。

2)使用DCM的PSR IC,工作频率在70KHz以下。

4:输出短路SCP后,SR MOS管温度高,输入瞬时功率增加

产生原因:

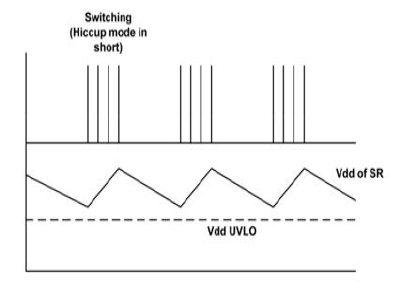

当输出端进入短路保护,初级IC进入HiccupMode,如果VCC供电不够的话,SR MOS进入UVLO欠压保护,那么Isd就流入MOS体内二极管,此时,SR MOS温度升高,输入瞬时功率相对增大。

解决对策:

- 选择Vo短路保护值低于Vdd_UVLO的SRIC;

- 如果SR IC没有Vo短路保护功能,可尝试增加Vcc电容容量。